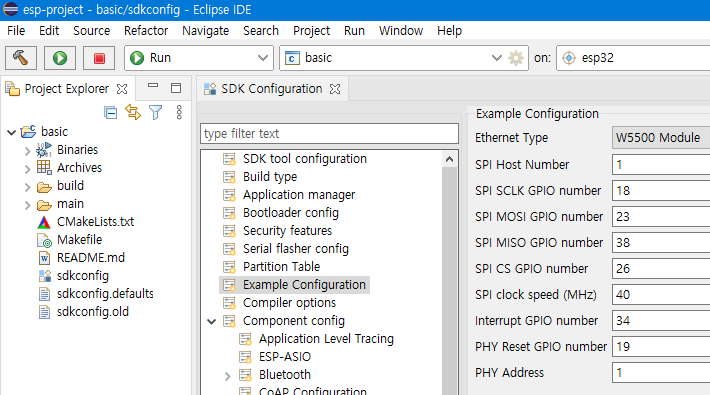

Used products are

M5Stack Core2 ESP32 IoT Development Kit for AWS IoT EduKit

and LAN Module W5500 with POE.

Softwares are esp-idf-master(v4.4) and esp-idf-tools-setup-online-2.7.exe

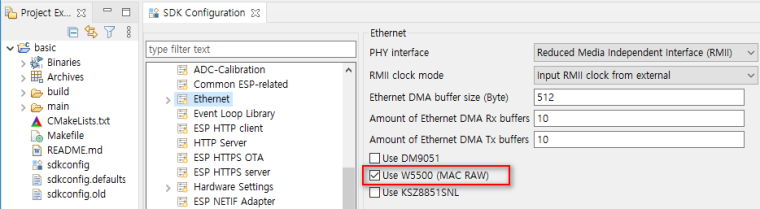

in the picture, "SPI MISO GPIO number is fixed "19",

I found all relevant sources and changed 19 to 38.

I compiled and download.

the core2 showed the following message.

E (363) spi_hal: spi_hal_cal_clock_conf(101): When work in full-duplex mode at frequency > 26.7MHz, device cannot read correct data.

Try to use IOMUX pins to increase the frequency limit, or use the half duplex mode.

Please note the SPI master can only work at divisors of 80MHz, and the driver always tries to find the closest frequency to your configuration.

Specify SPI_DEVICE_NO_DUMMY to ignore this checking. Then you can output data at higher speed, or read data at your own risk.

E (403) spi_master: spi_bus_add_device(368): assigned clock speed not supported

ESP_ERROR_CHECK failed: esp_err_t 0x106 (ESP_ERR_NOT_SUPPORTED) at 0x40085f10

file: "../main/ethernet_example_main.c" line 153

func: app_main

expression: spi_bus_add_device(CONFIG_EXAMPLE_ETH_SPI_HOST, &devcfg, &spi_handle)

abort() was called at PC 0x40085f13 on core 0

=========================================================================

Here is the full message of booting.

Rebooting...

I (12) boot: ESP-IDF v4.4-dev-1183-g9d34a1cd4 2nd stage bootloader

I (12) boot: compile time 14:59:17

I (12) boot: chip revision: 3

I (16) boot_comm: chip revision: 3, min. bootloader chip revision: 0

I (23) boot.esp32: SPI Speed : 40MHz

I (27) boot.esp32: SPI Mode : DIO

I (32) boot.esp32: SPI Flash Size : 16MB

I (36) boot: Enabling RNG early entropy source...

I (42) boot: Partition Table:

I (45) boot: ## Label Usage Type ST Offset Length

I (53) boot: 0 nvs WiFi data 01 02 00009000 00006000

I (60) boot: 1 phy_init RF data 01 01 0000f000 00001000

I (68) boot: 2 factory factory app 00 00 00010000 00100000

I (75) boot: End of partition table

I (79) boot_comm: chip revision: 3, min. application chip revision: 0

I (86) esp_image: segment 0: paddr=00010020 vaddr=3f400020 size=1079ch ( 67484) map

I (120) esp_image: segment 1: paddr=000207c4 vaddr=3ffbdb60 size=02590h ( 9616) load

I (125) esp_image: segment 2: paddr=00022d5c vaddr=40080000 size=0c9f0h ( 51696) load

I (148) esp_image: segment 3: paddr=0002f754 vaddr=50000000 size=00010h ( 16) load

I (149) esp_image: segment 4: paddr=0002f76c vaddr=00000000 size=008ach ( 2220)

I (155) esp_image: segment 5: paddr=00030020 vaddr=400d0020 size=313f8h (201720) map

I (245) boot: Loaded app from partition at offset 0x10000

I (245) boot: Disabling RNG early entropy source...

I (257) cpu_start: Pro cpu up.

I (257) cpu_start: Starting app cpu, entry point is 0x40081114

I (251) cpu_start: App cpu up.

I (271) cpu_start: Pro cpu start user code

I (272) cpu_start: cpu freq: 160000000

I (272) cpu_start: Application information:

I (276) cpu_start: Project name: ethernet_basic

I (282) cpu_start: App version: 1

I (286) cpu_start: Compile time: May 28 2021 15:28:52

I (292) cpu_start: ELF file SHA256: 3002b11df1bc5d6d...

I (298) cpu_start: ESP-IDF: v4.4-dev-1183-g9d34a1cd4

I (305) heap_init: Initializing. RAM available for dynamic allocation:

I (312) heap_init: At 3FFAE6E0 len 0000F480 (61 KiB): DRAM

I (318) heap_init: At 3FFC18B0 len 0001E750 (121 KiB): DRAM

I (324) heap_init: At 3FFE0440 len 00003AE0 (14 KiB): D/IRAM

I (330) heap_init: At 3FFE4350 len 0001BCB0 (111 KiB): D/IRAM

I (337) heap_init: At 4008C9F0 len 00013610 (77 KiB): IRAM

I (344) spi_flash: detected chip: generic

I (348) spi_flash: flash io: dio

I (353) cpu_start: Starting scheduler on PRO CPU.

I (0) cpu_start: Starting scheduler on APP CPU.

E (363) spi_hal: spi_hal_cal_clock_conf(101): When work in full-duplex mode at frequency > 26.7MHz, device cannot read correct data.

Try to use IOMUX pins to increase the frequency limit, or use the half duplex mode.

Please note the SPI master can only work at divisors of 80MHz, and the driver always tries to find the closest frequency to your configuration.

Specify SPI_DEVICE_NO_DUMMY to ignore this checking. Then you can output data at higher speed, or read data at your own risk.

E (403) spi_master: spi_bus_add_device(368): assigned clock speed not supported

ESP_ERROR_CHECK failed: esp_err_t 0x106 (ESP_ERR_NOT_SUPPORTED) at 0x40085f10

file: "../main/ethernet_example_main.c" line 153

func: app_main

expression: spi_bus_add_device(CONFIG_EXAMPLE_ETH_SPI_HOST, &devcfg, &spi_handle)

abort() was called at PC 0x40085f13 on core 0

Backtrace:0x400d2fcf:0x3ffb24e00x40085f21:0x3ffb2500 0x4008b7f6:0x3ffb2520 0x40085f13:0x3ffb2590 0x400d87d8:0x3ffb25b0 0x401010e9:0x3ffb2690 0x40088b41:0x3ffb26b0